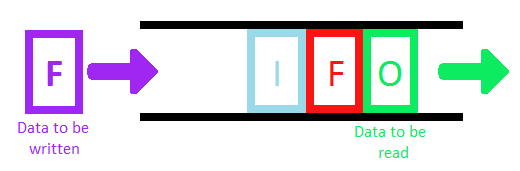

How FIFO buffers are used to transfer data and cross clock domains.

The acronym FIFO stands for First In FIrst Out. FIFOs are used everywhere in FPGA and ASIC designs, they are one of the basic building blocks. And they are very handy. FIFOs can be used for any of these purposes.

Purposes

- Crossing clock domains

- Buffering data before sending it off chip( to DRAM or SRAM)

- Buffering data for software to look at some later time

- Storing data for later processing

About FIFO

- Can be made of registers or BRAM

- Register based = small / BRAM = big

- Has Width and Depth

- Synchronous

- Can use unique or shared clock

FIFO Tips

- Golden Rules

1. Never write to Full FIFO( overflow)

2. Never read from Empty FIFO( underflow)

- Figure out how to write code using AE/AF/Empty/Full flags

- Never rely on FIFO level count

- Can be created via

1. Instantiation

2. Inference *recommended*

3. GUI Tools

- First Word Fall Through is great

- Link to register FIFO in description

A general tip I have is figure out how to write code using almost empty almost full if you figure out how to write dfficient code just using those four flags you spend some time thinking about it you'll be extremely successful.

I mentioned before that FIFOs have a level count associated with them usually a lot of FPGAs will be like here is. This handy thing you can figure out exactly how many words during the FIFO you know how many you can read out don't use it. It's evil.

'Semiconductor > ASIC & FPGA' 카테고리의 다른 글

| Metastability (0) | 2020.10.31 |

|---|---|

| What is a FPGA Latch? (0) | 2020.10.21 |

| Looping Statements (0) | 2020.10.21 |

| Synthesizable vs Non-Synthesizable code (0) | 2020.10.18 |

| How Flip-Flops work in FPGAs? (0) | 2020.10.18 |