Metastability

Asynchronous clock간 신호를 교환 할 시 보통 Flip-Flop 2개를 연달아 지나가도록 설계합니다. 이러한 방법으로 Metastability를 피할 수 있다고 하며 Metastability란 간단히 Low-level도 High-level도 아닌 중간 상황이 지속되는 것을 말합니다. 이것 말고 unknown이라는것도 있는데 이것은 말 그대로 Low인지 High인지 모르지만 둘 중 하나인것입니다.

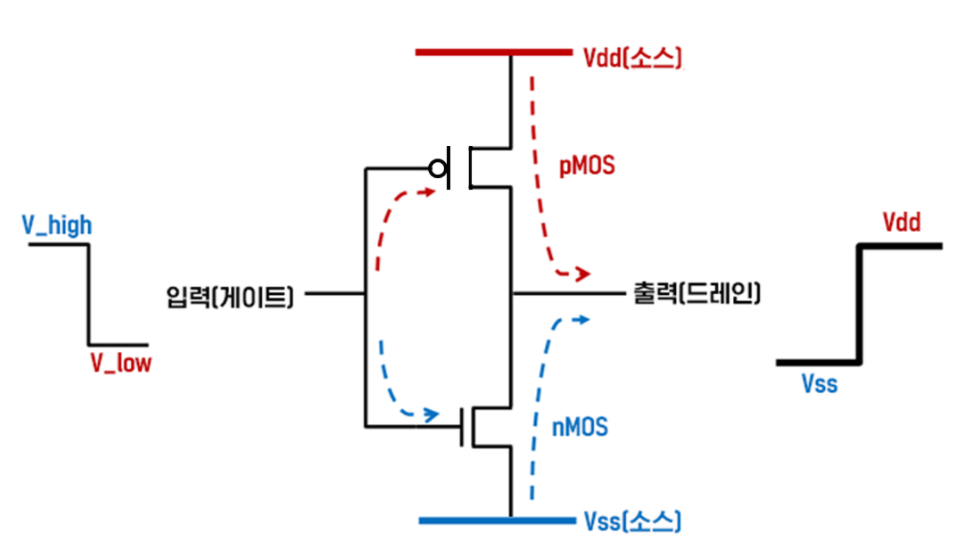

Metastability는 중간값을 가지는 것이 문제입니다. 문제가 되는 이유는 CMOS 회로는 간단하게 PMOS로 이루어져 VDD로 출력을 연결하는 PULL-UP회로와 NMOS로 이루어져서 출력을 GROUND로 연결하는 PULL-DOWN회로로 구성됩니다. 그래서 일반적인 Low혹은 High 입력에 대하여 PULL-UP만 ON되고 PULL-DOWN은 OFF 혹은 그 반대 상황이 되는것이 우리가 원하는 상황입니다. 단지 입력이 바뀌는 순간에만 순간적으로 PULL-UP과 PULL-DOWN이 모두 부분적으로 ON이 되어 VDD에서 GROUND로 전류가 순간적으로 많이 흐르게 됩니다.

그래서 입력이 Low 혹은 High 어느쪽으로 명확하게 지속되어야지 중간값으로 오래 지속되면 power 문제 뿐 아니라 회로가 타는 등의 문제가 발생할 수도 있어 피해야 하는 것입니다. 그런데 Asynchronous clock 간에 신호를 교환하게 되면 정확하게 값이 변화하는 중간에 다른 clock에서 동작하는 Flip-Flop이 값을 Capture하게 되어 중간값이 지속될 수 있습니다. 이때 출력이 중간값을 유지하는 것은 사실 매우 불안정한 상황입니다. 그래서 약간의 노이즈가 있다던가 회로가 정확히 비례하지 않는다던가 하는 이유로 Low 혹은 High 어느 한 쪽으로 결정되게 됩니다. 문제는 그것이 순간적으로 일어나지 않고 서서히 진행되는 것에 있습니다.

그렇기 때문에 Flip-Flop을 하나 더 거치게 하여 Clock cycle만큼 시간을 벌어주는 것입니다. 첫 번째 Flip-Flop을 거친 출력이 두 번째 Flip-Flop의 입력이 되어 Capture되기 까지 1-clock 시간동안 Low 혹은 High로 완전히 결정되라는 것입니다. 이것을 Flip-Flop은 항상 Low나 High의 출력을 낸다라고 오해해선 안됩니다. 그렇다면 2개의 Flip-Flop을 달 이유가 없는 것이기 때문입니다.

Multi-bits

Multi-bits 신호를 전달할 때는 단순히 각각의 bit마다 Flip-Flop 2개를 설계하는 구조를 선택해서는 안됩니다. Multi-bits 신호라면 각각의 bit이 변하는 시간도 다르고 동시에 변한다 하더라도 각각 bit이 Low 혹은 High로 갈지 모르기 때문에 전혀 엉뚱한 값이 전달될 수 있기 때문입니다.

예를 들어, 0000인 신호가 1111로 바뀌었는데 모두 Metastability이거나 0101이 되거나 0011이 된다면 우리가 원하는 결과가 아니게 됩니다. 변하는 순간에 신호가 0000 혹은 1111 둘 중 하나라면 별 문제가 없지만 0101 혹은 0011은 전혀 발생하면 안되는 상황이기 때문입니다. 따라서 이러한 문제를 피할 수 있는 방법을 고안해야 합니다.

2가지 방법이 있는데 하나는 Handshake 방법이고 또 다른 방법은 Gray code를 이용하는 방법입니다. Hanshake 방법이란 신호를 전송하는 쪽에서 신호를 보낸다는 신호를 보내고 받는 쪽에서 신호를 받았다고 신호를 보내어 서로 신호를 주고 받는 중간에 신호가 바뀌는 일이 없도록 보장하는 것입니다. 보통 req, ack 신호를 서로 교환해서 처리를 합니다.

Gray code란 한 번에 한 bit만 변화하도록 만든 code를 말합니다. 0000, 0001, 0011, 0010 순서로 바뀌도록 만든 것입니다. 이 Gray code를 이용할 때도 역시 Flip-Flop 2개의 구조로 사용하지만 이러한 경우에는 문제가 발생하지 않습니다. 0001에서 0011로 바뀌는 순간이 Capture 되었다고 하면 0에서 1로 바뀐 2번째 bit만 Metastability 상태가 됩니다. 나머지 bit들은 상태가 바뀌지 않기 때문에 결국 2번째 Flip-Flop의 결과는 0001혹은 0011로 별 문제가 없는 상황이 됩니다.

How to prevent Metastability

Most metastable conditions occur in one of two ways

- You are sampling a signal external to the FPGA

- You are crossing clock domains

Both of these situations can be fixed the same way. Whenever you are encountering a situation that might introduce Metastability you can simply Double-Flop your data.

In the figure to the above, a signal that is asynchronous to the clock is being sampled by the first Flip-Flop. This will create a metastable condition at the output. If you again sample this output, you can now fix your metastable event. The output of the second Flip-Flop will be stable.

'Semiconductor > ASIC & FPGA' 카테고리의 다른 글

| Propagation Delay (0) | 2020.11.08 |

|---|---|

| Shift Register (0) | 2020.11.08 |

| What is a FPGA Latch? (0) | 2020.10.21 |

| What is a FIFO in an FPGA? (0) | 2020.10.21 |

| Looping Statements (0) | 2020.10.21 |