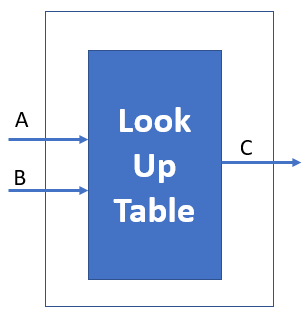

It should be noted that all of those discrete logic gates that actually do not physically exist inside of an FPGA. However, it is possible to perform those functions. The way that FPGAs are able to do Boolean algebra is by using Look-up Tables. A Loop-up Table is a discrete block of functionality that can be programmed by the Digital Designer. LUTs use the same truth table concept to relate outputs to inputs.

As was mentioned in the beginning of this article, discrete logic gates do not actually exist inside of an FPGA. Instead FPGAs use Loop-up Tables or LUTs. The LUT is programmed by the Digital Designer to perform a Boolean algera equation. As you might expect, all possible combinations of Boolean expressions need to be able to be programmed into the LUTs. I will say that again a different way: one 3-Input LUT can make any Boolean algebra equation you can think of using 3 input signals.

LUTs can come in different sizes depending on the FPGA that you are using, but they all behave the say way. 3-input LUTs were the norm not too long ago, but today 4-input and even 5-input LUTs are common. If you need to make a more complicated expression, you can just use more Look-Up Tables. LUTs are one of the two most fundamental components in an FPGA. A single FPGA has thousands of these components. Now that you are familiar with these wonderfully versatile components, it is time to discuss the other most important element inside of an FPGA.

Look-Up Table can implement any Boolean algebra equation with three inputs LUT, they can be four inputs LUT and sometimes even a five inputs LUT. When you turn on the FPGA LUTs get programs all the individual Boolean algebra equations that needed inside of the FPGA.

- LUT( Loop Up Table)

FPGA는 Gate Array와 달리 NAND or NOR은 사용하지 않고 대신 LUTs를 사용하여 조합회로를 구성합니다. LUT란 메모리라고 생각하면 되며 Address에 입력을 가하면 메모리 내부의 내용이 출력으로 나오고 그 자체가 Logic이 됩니다. 메모리 내부의 내용을 바꾸어 다양한 조합회로를 구현할 수 있습니다. 순서회로를 설계할 수 있어야 하므로 LUT의 끝에는 Flip-Flop이 달려 있는 구조입니다. 기본적으로 LUT를 여러개 넣은 것을 한 단위로 하여 Vendor 별로 Slice 혹은 ALM으로 부르며 그것의 배열이 FPGA를 이루고 있습니다.

'Semiconductor > ASIC & FPGA' 카테고리의 다른 글

| Looping Statements (0) | 2020.10.21 |

|---|---|

| Synthesizable vs Non-Synthesizable code (0) | 2020.10.18 |

| How Flip-Flops work in FPGAs? (0) | 2020.10.18 |

| What is a Digital Designer? (0) | 2020.10.16 |

| What is an FPGA (0) | 2020.10.16 |